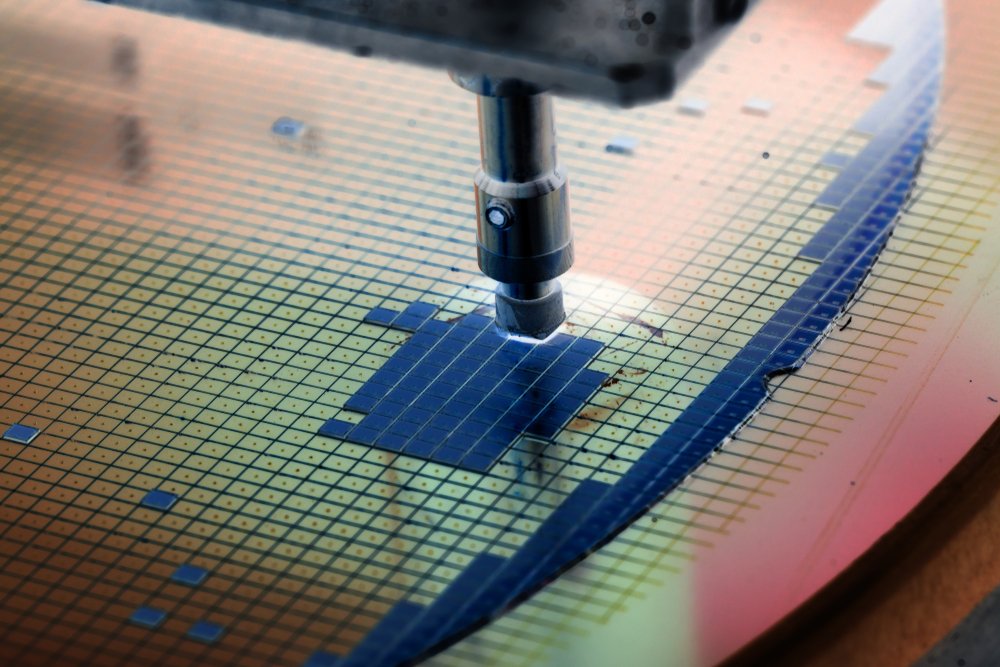

AMD cuit ses puces Ryzen en 3 nm, les dernières puces Cure Ultra d’Intel sont construites en 1,8 nm ou 18 angströms. Que signifient exactement ces nanomètres et que disent-ils réellement sur les performances d’une puce ?

Les processeurs Core Ultra de troisième génération d’Intel, ou Panther Lake, sont fabriqués selon le processus de cuisson 18A d’Intel. 18 représente 18 angströms, soit 1,8 nanomètre. AMD fait construire ses CPU Ryzen dans les usines de TSMC, en 3 nm. Dans un avenir proche, AMD adoptera le 2 nm chez TSMC.

Il y a pas mal de passes d’armes entre Intel et TSMC concernant ces désignations en nanomètres. Ce qu’Intel appelle 18A serait par exemple identique à ce que TSMC décrit comme 5 nm. La distinction est importante : la taille d’un nœud de production a un impact direct sur les performances des puces. Maintenant qu’Intel, avec Panther Lake, reprend une place à l’avant-garde technologique et qu’AMD s’est révélé être un concurrent redoutable, nous examinons ce que signifient réellement ces nanomètres.

À propos des nœuds

Le nom générique de la technologie utilisée pour fabriquer une puce est un « nœud ». Les nœuds se distinguent les uns des autres par une désignation en nanomètres. 7 nm, 5 nm, 3 nm… sont donc des nœuds de production. Ils donnent une indication de la précision du processus de production dans une usine. Intel possède par exemple des usines de puces qui produisent des puces sur un nœud de 4 nm, ce qui signifie que ces puces sont fabriquées avec un ensemble de technologies modernes qui relèvent de l’appellation « 4 nm ».

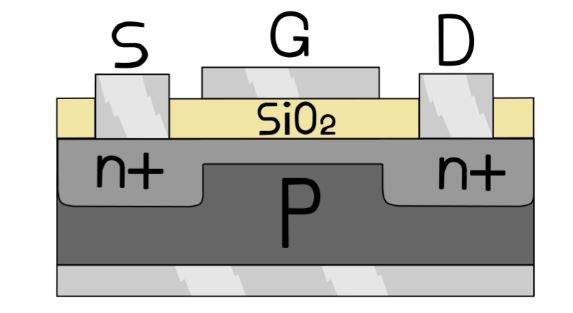

Une idée fausse répandue est que les nanomètres se rapportent à la taille des transistors sur une puce. Ce n’est plus le cas aujourd’hui. Jusqu’en 1997, il y avait bien un lien direct entre la taille d’un transistor et la dénomination d’un nœud. Plus précisément, un nœud correspondait à la longueur de la porte du transistor produite avec la technologie.

Le nœud de 350 nm en 1995 a reçu son nom en raison des puces avec des transistors ayant une longueur de porte de 350 nm, qui sortaient de la chaîne de production du nœud de 350 nm. Autour du tournant du siècle, ce lien a été perdu. De nouvelles technologies pour la construction de microtransistors ont conduit à une densité de transistors plus élevée sur les micropuces, rendant la longueur de la porte moins pertinente.

Moins d’acteurs, plus de différences

Jusqu’en 2013 environ, il y avait une unanimité dans le monde des processeurs sur ce qu’un nœud spécifique devait impliquer précisément. Comme il faut en moyenne près de quinze ans pour que la technologie passe d’un article scientifique à une usine de puces opérationnelle, il existait jusqu’alors un organisme sectoriel global qui élaborait des feuilles de route à long terme pour les nœuds de processeurs. L’International Technology Roadmap for Semiconductors, ITRS pour les intimes, fixait pour chaque nœud des objectifs concernant le nombre de transistors par puce et la taille moyenne des composants sur une telle puce.

ITRS a été supprimé en 2017, bien qu’il existe un successeur avec l’International Roadmap for Devices and Systems (IRDS). Son importance est moindre. Logique : alors que les puces étaient auparavant construites dans les usines d’une dizaine de fabricants, il n’y a plus aujourd’hui que trois entreprises capables de mettre en place des lignes de production avec la technologie la plus moderne : Intel, Samsung et TSMC.

Détourné par le marketing

Si la désignation en nanomètres ne correspond plus à un composant spécifique sur une puce, et qu’elle n’est pas non plus une appellation générique sous laquelle se cachent des conventions en matière de taille et de technologie, quelle est encore la valeur de notions telles que nm et 3 nm ?

La dénomination en nanomètres pour les nœuds est aujourd’hui reprise par le département marketing.

Techniquement, très peu. La désignation en nanomètres pour les nœuds est aujourd’hui reprise par le département marketing et n’a plus de rapport direct avec les composants d’une micropuce. Si Intel passe de 4 nm à 3 nm, voire à 1,8 nm, on ne peut pas en déduire ce qui se passe exactement dans le processus de production.

Terme indicatif

La taille du nœud est donc aujourd’hui plutôt une indication qu’un fabricant de puces a équipé ses usines d’une nouvelle technologie, qui est plus précise à différents niveaux et permet une densité de transistors plus élevée. Le degré de précision n’est pas tout à fait clair. Historiquement, un nouveau nœud devait s’accompagner d’un doublement du nombre de transistors sur une surface donnée, mais cette règle empirique n’est aujourd’hui guère plus qu’une indication approximative. Lorsqu’un nœud passe de la taille X à la taille Y, le fabricant indique surtout qu’un grand bond en avant a été fait dans son propre processus de production.

Ce processus de production diffère plus que jamais entre les différentes usines. Intel construit ses puces différemment de TSMC et Samsung. Différentes technologies liées à un changement d’échelle sont introduites à différents moments (FinFET, RibbonFET, Gate-last…). Cela signifie qu’un concepteur de puces doit aujourd’hui travailler en étroite collaboration avec le fabricant de son choix.

Les conceptions de puces doivent plus que jamais être optimisées non seulement pour le nœud utilisé, mais aussi pour l’implémentation de ce nœud par TSMC, Intel ou Samsung. Quiconque veut faire fabriquer dans une usine de TSMC un design conçu pour Samsung, par exemple, sur un nœud similaire, peut s’attendre à une petite année de reconceptions.

Comparaison

Si l’on regarde un seul fabricant, la désignation d’un nœud reste précieuse. 3 nm est mieux que 5 nm, et les améliorations sont suffisamment importantes pour que le fabricant de puces parle d’un nouveau nœud. En règle générale, cela signifie des composants plus compacts sur la puce, ce qui améliore les performances. Nous expliquons plus loin dans l’article pourquoi c’est le cas. En tout cas, on peut affirmer sans aucun doute que les puces Panther Lake 1,8 nm d’Intel sont structurellement supérieures aux processeurs Arrow Lake 3 nm.

3 nm, c’est mieux que 5 nm. Une surprise ?

Il est devenu plus difficile de faire une comparaison entre les fabricants. Les puces Ryzen 3 nm d’AMD sont cuites par TSMC. Un nœud plus petit permet d’obtenir de meilleures puces, mais les noms de nœuds sont la propriété du département marketing. Le 3 nm chez TSMC est-il donc réellement plus petit que, par exemple, le 4 nm chez Intel ?

Les chiffres derrière le nœud

Pour étudier une telle affirmation, nous devons rechercher des paramètres plus objectifs. Concrètement, il s’agit du Contacted Gate Pitch et du Minimum Metal Pitch. Le Gate Pitch est grosso modo la distance minimale entre les transistors sur une puce, tandis que le Metal Pitch est la distance minimale entre les interconnexions qui relient les transistors aux circuits logiques.

Une distance plus petite entre les transistors implique une densité de transistors plus élevée, une distance plus petite entre les interconnexions signifie que vous pouvez également connecter les transistors supplémentaires à des circuits plus complexes.

Pour plus de clarté, nous examinons les nœuds 3 nm et 4 nm d’Intel et de TSMC. Le nœud N4 de TSMC a un gate pitch de 51 nm et un metal pitch de 28 nm. Intel 4 a des chiffres similaires avec 50 nm et 30 nm. Pour le nœud TSMC N3E, le gate pitch diminue à 48 nm et le metal pitch à 23 nm. Pour le nœud Intel 3, nous restons bloqués à 50 nm et 30 nm.

Il en ressort que ce qu’Intel appelle Intel 3 et Intel 4 se rapproche de TSMC N3E et TSMC 4. La différence entre 4 nm et 3 nm n’est que faible dans les deux cas, ce qui implique que la réduction de nœud de 4 nm à 3 nm a également été en partie motivée par le marketing.

Pour Intel 18A et TSMC N2, la comparaison est plus difficile à faire. TSMC obtiendrait avec N2 une densité plus élevée qu’Intel 18A (238 MTx/mm² vs 313 MTx/mm² – million de transistors par millimètre carré). Intel 18A pourrait alors fournir plus de performances. Il semble en tout cas que les deux nœuds seront à égalité, même si Intel suggère avec la désignation 18A qu’il a une longueur d’avance.

Plus petit, mais pourquoi meilleur ?

Nous arrivons ainsi enfin au cœur du problème : pourquoi plus petit est-il meilleur ? Une densité plus élevée (dont Contacted Gate Pitch et Minimum Metal Pitch sont de bons paramètres objectifs) va généralement de pair avec des transistors plus petits. Un transistor plus petit a une distance plus petite entre la source et le drain. Cela signifie qu’une tension plus faible est nécessaire pour faire passer le transistor de 0 à 1 et inversement.

Une puce avec un design identique, cuite sur un nœud plus petit, consommera donc moins de courant que son prédécesseur. Cela a d’une part un impact direct sur l’autonomie de la batterie des ordinateurs portables, mais permet d’autre part d’améliorer les performances. En effet, la baisse de la consommation entraîne également une diminution de la chaleur générée.

Comme les puces sur un nœud plus petit fonctionnent intrinsèquement plus froidement que les puces identiques construites sur un nœud plus grand, elles peuvent supporter des fréquences légèrement plus élevées à un même TDP (thermal design point = consommation électrique maximale). L’architecture (modifications de la conception de la puce qui ne concernent pas le nœud) a également un impact, mais il est plus faible.

Tirer des conclusions

On peut donc affirmer qu’Intel Panther Lake (Intel 18A) est intrinsèquement meilleur que Meteor Lake (Intel 4), sans connaître les détails du nœud : plus petit est physiquement toujours meilleur. Les puces sont toutes deux cuites dans les usines d’Intel et sont donc comparables entre elles.

Pour la même raison, on ne peut pas dire grand-chose sur Panther Lake par rapport aux puces AMD cuites sur le nœud TSMC 2N. 1,8 nm semble plus petit que 2 nm, mais comme nous l’avons expliqué en détail ci-dessus, ce n’est pas toujours vrai dans le monde des processeurs.

Cet article a été publié initialement le 29 août 2019. Il a été mis à jour avec les informations les plus récentes.